On February 10, 2026, the China Electronics Standardization Institute (CESI), the secretariat of the National Integrated Circuits (IC) Standardization Technical Committee (SAC/TC599), released the committee’s 2025 Annual Highlights.

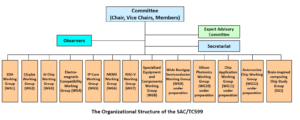

SAC/TC599, comprising 57 committee members, 172 observers, and over 700 working group members in its first term starting from November 2022, is responsible for standardization across the entire IC industry chain, including design, manufacturing, packaging, testing, application, and equipment. It mirrors the subcommittees of IEC/TC47(Semiconductor Devices): SC47A on Integrated Circuits, SC47D on Semiconductor Devices Packaging, and SC47F on MEMS.

To better address the evolving needs of the industry, SAC/TC599 expanded its technical working groups in 2025. Four new working groups were formally established, focusing on IP Cores (WG5), MEMS (WG6), RISC-V (WG7), and dedicated IC equipment and components (WG8). Additionally, preparations were initiated for four more groups: Wide Bandgap Semiconductors (WG9), Silicon Photonics (WG10), Chip Applications (WG11), and Automotive Chips (WG12), alongside a study group for Brain-inspired computing Chips (SG1). This expansion provides a robust framework to cover key segments of the IC industry chain. The current organizational structure is shown below.

By the end of 2025, SAC/TC599 has managed over 400 standards, with 209 published (158 national standards, 51 sector standards) and driven China-led efforts resulting in 12 published international standards, with another 6 currently in development. Throughout 2025, the committee published 26 new standards, including 19 national standards covering areas like chiplets, packaging, and automotive chips, and 7 sector standards focused on areas such as AI chip testing and analog/digital chip design. A major 2025 achievement was the release of five critical national standards for chiplet interconnection interfaces. The standard series GB/T 46280-2025 Specification for chiplet interconnection interface includes Part 1: General Principles, Part 2: Protocol layer technical requirements, Part 3: Data link layer technical requirements, Part 4: Physical layer technical requirements based on 2D package, and Part 5: Physical layer technical requirements based on 2.5D package. These standards define the layered architecture, functional requirements, and data transmission mechanisms for chiplet interconnection. They support various interconnect scenarios, package types, and bus protocols, achieving core technical indicators recognized as internationally competitive.

In 2025, SAC/TC599 made notable progress in international standardization. It facilitated the publication of 4 China-led MEMS standards and the approval of 4 new MEMS projects and proposed 3 AI chip initiatives at IEC/SC47A. The committee also hosted the IEC/SC47F MEMS working group meeting and workshop, and recommended 15 Chinese experts as IEC registered experts, strengthening talent foundations for continued international engagement.

2025 marked a year of systematic execution for SAC/TC599, as it established standards for chiplets and new working groups for RISC-V and automotive chips, signaling China’s drive to build a self-reliant IC ecosystem through standardization. While European firms hold traditional strengths in sectors like automotive semiconductors, China is accelerating its development via standardization. As China refines its standards, domestic supply chain autonomy strengthens. Consequently, European firms may face stricter localization requirements in China and encounter more competitive Chinese products globally. Therefore, European enterprises should accelerate innovation and adopt more proactive and flexible standardization strategies to remain competitive.